# DECODER PENYANDIAN SALURAN HDB3 BERBASIS FPGA

Sahbuddin Abdul Kadir<sup>1)</sup>, Zaini<sup>2)</sup> <sup>1,2)</sup>Dosen Jurusan Teknik Elektro Politeknik Negeri Ujung Pandang, Makassar

#### **ABSTRACT**

In digital communication systems, information is represented in the form of zero and one bit. For some distance, this representation may be identified on the receiver. Conversely for long distance will cause dc component problems and synchronization. High Density Bipolar-3 zero (HDB3) encoding is one of the scrambling techniques that adapt the Alternate Mark Inversion (AMI) encoding problem in the synchronization process for long zero bit sequences. In this study designed Decoder HDB3 line coding using FPGA with System on Chip (SoC) method. The results of this study show that by adding non-zero insertion bits to long zero bit sequences, no longer form a straight line that resembles noise. But like the actual display of bits but does not follow the AMI algorithm that makes each bit one opposite the polarity. So it is easier to recovery the bits of information on the receiver.

Keywords: Sincronization, Scrambling, AMI, HDB, SoC

#### 1. PENDAHULUAN

Pada sistem komunikasi digital, informasi direpresentasikan dalam bentuk bit nol dan satu. Namun representasi ini menimbulkan masalah komponen dc yang merupakan *amplitude* rata-rata bit yang tidak nol. Sehingga tidak dapat digunakan pada media yang tidak dapat melewatkan komponen dc. Selain itu, pada runtun bit nol atau satu yang panjang menyebabkan hilangnya sinkronisasi. Karena bila sinyal tidak bervariasi, maka penerima tidak dapat membedakan mana yang awal dan akhir dari tiap-tiap bit. Oleh karena itu diperlukan teknik penyandian yang bukan sekedar merepresentasikan informasi ke dalam bit nol dan satu, tetapi memiliki kualifikasi yang diidentifikasi pada penerima. Teknik penyandian ini dikenal teknik *scrambling* mengadaptasi teknik penyandian saluran untuk mengatasi permasalahan sinkronisasi. Teknik ini sering digunakan untuk layanan transmisi jarak jauh menggunakan penyandian *High Density Bipolar-3 Zeros* (HDB3) dan *Bipolar With 8-Zeros Substitution* (B8ZS). Penyandian HDB3 merupakan modifikasi penyandian *Alternate Mark Inversion* (AMI) yang bermasalah pada proses sinkronisasi untuk runtun bit nol yang panjang dengan menyisipkan bit yang tidak nol pada setiap runtun bit nol yang lebih dari tiga. Tetapi komponen de sudah tidak terlihat lagi pada penyandian saluran AMI dengan menggunakan polaritas yang berlawanan pada setiap bit satu dan tegangan 0V untuk bit nol.

# 2. METODE PENELITIAN

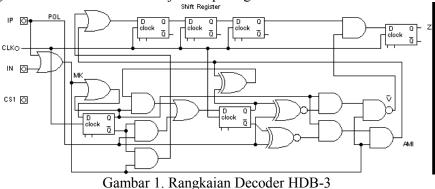

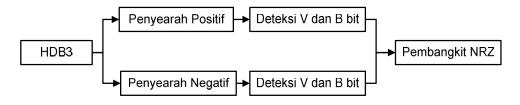

Metode penelitian yang digunakan pada panelitian ini adalah Sistem *on Chip*. Desain dilakukan dengan bahasa pemrograman HDL verilog sedangkan implementasi menggunakan FPGA. Rangkaian *decoder* HDB-3 akan melakukan proses yang sebaliknya pada *encoder*. Rangkaian ini akan mendeteksi runtun bit 000v dan b00v. Kemudian runtun bit tersebut dikembalikan menjadi runtun nol. Sedangkan polaritas bit satu yang negatif disearahkan dengan polaritas bit satu yang negatif. Sehingga diperoleh sinyal dengan runtun bit nol dan satu tanpa v dan b bit yang sama dengan bit yang dikodekan pada penerima setelah melalui proses sinkronisasi. Rangkaian Decoder HDB-3 ditunjukkan pada gambar 1.

<sup>&</sup>lt;sup>1</sup> Korespondensi: Sahbuddin Abdul Kadir, Telp 085299095195, sahbuddin.ak@poliupg.ac.id

#### **Detektor Polaritas**

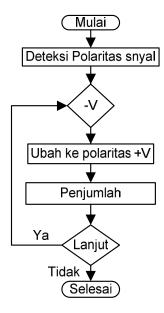

Pada output sinyal HDB-3 terdapat tiga level tegangan yaitu +V, 0, -V. Sedangkan polaritas pada sinyal NRZ hanya menggunakan dua level tegangan yaitu +V dan 0. Maka pada *decoder* HDB3 sinyal dengan polaritas negatif akan dikembalikan ke polaritas positif melalui detektor polaritas ditunjukkan pada gambar 2.

Gambar 2. Flowchart detektor polaritas.

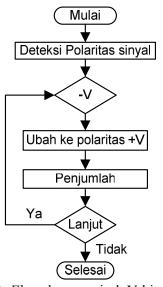

#### Pemisahan V-bit

Jika pada *encoder* HDB3 V-bit dibangkitkan jika terdapat runtun bit 0 yang lebih dari tiga, baik pada saat jumlah bit 1 ganjil atau genap. Maka pada *decoder* HDB3 V-bit diperlakukan sebaliknya atau dipisahkan dari runtun bit informasi atau yang bukan bit sisipan. Hasil pemisahan V-bit diperoleh deretan pulsa yang masih mengandung B-bit tetapi sudah menggunakan dua polaritas tegangan yang menjadi bentuk dasar sinyal NRZ. *Flowchart* pemisah V-bit ditunjukkan pada gambar 3.

Gambar 3. Flowchart pemisah V-bit

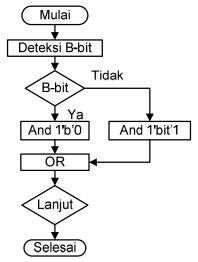

# Pemisahan B-bit

Proses pemisahan B-bit pada *decoder* HDB3 dilakukan sama seperti pada proses pemisahan V-bit, tetapi posisi bit yang berbeda. V-bit berada pada bit yang ke empat runtun 4 bit 0. Sedangkan B-bit berada pada bit pertama runtun 4 bit 0. Proses pemisahan B-bit juga akan menghasilkan sinyal dengan dua polaritas tegangan. Sinyal ini merupakan sinyal NRZ tetapi belum sinkron dan setelah melalui proses sinkronisasi akan

diperoleh sinyal yang sama dengan sinyal NRZ pada *encoder* HDB3. *Flowchart* pemisah B-bit ditunjukkan pada gambar 4.

Gambar 4. Flowchart pemisah B-bit

# Pembangkit Sinyal NRZ

Pada pembangkit sinyal NRZ berfungsi untuk membentuk dua level tegangan,-V dan +V. Pada bit 0 menyatakan tegangan yang lebih rendah dan bit 1 menyatakan tegangan yang lebih tinggi. Hasil yang diperoleh adalah siinyal NRZ yang sudah mengalami proses sinkronisasi.

# Rangkaian Decoder HDB-3

Rangkaian *decoder* HDB-3 berfungsi untuk mengubah sinyal HDB-3 menjadi sinyal NRZ. Dari beberapa rangkaian di atas, maka dapat diintegrasikan untuk menghasilkan rangkaian *decoder* HDB-3 seperti pada gambar 5.

Gambar 5. Blok Diagram Sistem Modul Decoder HDB-3

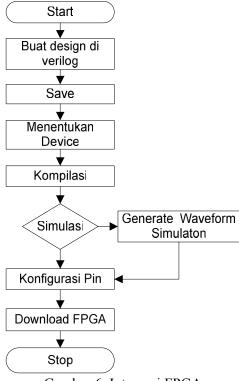

Proses perancangan panyandian HDB3 dilakukan dengan metode sistem *on chip* menggunakan bahasa pemrograman Verilog HDL yang diintegrasikan pada FPGA sebagai implementasi perangakat keras penyandian HDB3.

# 3. HASIL DAN PEMBAHASAN

Hasil perancangan penyandian *decoder* HDB3 diintegrasikan ke *board* FPGA menggunakan program aplikasi *quartus*. Integrasi dimulai dengan *compile* kode verilog penyandian HDB3 untuk memeriksa jika terjadi kesalahan pemrograman. Setelah itu dilakukan simulasi untuk melihat keluaran hasil rancangan sudah sesuai dengan input yang diberikan. Sebelum diimplementasikan ke *board* FPGA, dilakukan konfigurasi pin sebagai port input dan output implementasi penyandian HDB3. Sehingga tersedia port untuk pengukuran dan pengujian.

Gambar 6. Integrasi FPGA

# **Penyearah Polaritas**

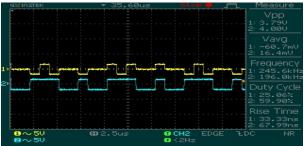

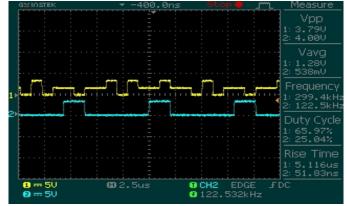

Penyearah polaritas sinyal berfungsi untuk mengembalikan polaritas negatif ke positif sehingga polaritas sinyal berada pada tegangan 0 dan +V seperti pada gambar 7 data HDB3 *channel* 1 dan NRZ dengan V-bit dan B-bit *channel* 2.

Gambar 7. Data HDB3 dan NRZ 11000000 dengan V-bit dan B-bit

Output rangkaian penyearah polaritas ini menghasilkan sinyal dengan dua level tegangan yaitu +V dan 0, tetapi masih mengandung B-bit dan V-bit.

# Pemisahan V-bit

Pemisahan V-Bit pada *decoder* HDB3 dilakukan untuk menghilangkan sisipan bit pada runtun bit 0 yang lebih dari 3. Hasil pemisahan V-Bit ini, diperoleh deretan pulsa yang masih mengandung B-bit tetapi sudah menggunakan dua polaritas tegangan yang menjadi bentuk dasar sinyal NRZ seperti pada gambar 8.

Gambar 8. Output HDB3 (11000000) dan pemisahan V-bit

#### Pemisahan B-bit

Pada rangkaian pemisahan B-bit *decoder* HDB3 dilakukan sama seperti pada proses pemisahan V-bit, tetapi posisi bit yang berbeda. V-bit berada pada bit yang ke empat runtun 4 bit 0. Sedangkan B-bit berada pada bit pertama runtun 4 bit 0. Proses pemisahan B-bit juga akan menghasilkan sinyal dengan dua polaritas tegangan. Sinyal ini merupakan sinyal NRZ yang telah dipulihkan setelah melalui proses sinkronisasi sinyal dan sama dengan sinyal NRZ pada encoder HDB3.

Gambar 9. Output encoder (11000000) dan pemisahan B-bit decoder HDB3

### Sinkronisasi

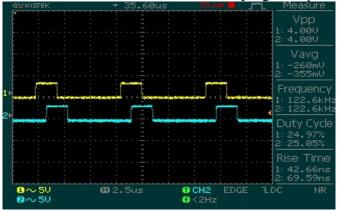

Hasil dari proses pemisahan B-bit telah memperlihatkan sinyal NRZ sebagai output decoder HDB3. Tetapi diperlukan proses sinkronisasi untuk memberikan durasi bit yang sama pada encoder.

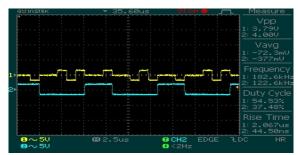

Gambar 10. Input encoder (11000000) dan output decoder HDB3 (NRZ)

Output dari proses sinkronisasi ini merupakan hasil akhir dari penelitian ini pada gambar 10. Channel 1 adalah sinyal NRZ input encoder HDB3 (11000000) dan channel 2 sinyal NRZ keluaran decoder HDB3.

Data input NRZ 11000000 sebagai *test-bench* pada penelitian ini digunakan untuk memperlihatkan output setiap tahapan pengujian penyandian saluran HDB3 pada FPGA. Karena pada B-bit hanya dibangkitkan pada runtun bit 1 genap. Sedangkan V-bit dibangkitkan pada setiap runtun bit 1 ganjil atau genap saat runtun bit 0 lebih dari 3. Hasil penelitian ini memperlihatkan jika terdapat runtun bit 0 yang lebih dari 3, akan digantikan dengan bit 1 pada awal dan akhir dengan 000V atau B00V yang tidak mengikuti algoritma penyandian AMI sebagai indikasi jika bit tersebut bukan bit 1 yang sebenarnya. Bit ini ditambahkan untuk menghindari runtun bit 0 yang sangat panjang dan berakibat pada hilangnya sinkronisasi. Bit yang disisipkan akan menjaga variasi sinyal pada runtun bit nol yang lebih dari 3 untuk membedakan awal dan akhir tiap-tiap bit.

### 4. KESIMPULAN

Teknik *scrambling* dapat mengatasi sinkronisasi runtun bit 0 yang panjang dengan subtitusi bit 1 pada runtun bit 0 yang lebih dari 3 (HDB3). Bit yang disisipkan akan menjaga variasi sinyal pada runtun bit nol yang lebih dari 3 untuk membedakan awal dan akhir tiap-tiap bit. Sehingga memungkinkan proses sinkronisasi bit yang ditrasmisikan.

# 5. DAFTAR PUSTAKA

Ali, Imran and Ahmad, Ali. 2013. An Efficient FPGA Based HDB3 Decoding System Using, *International Journal of Future Computer and Communication* Vol. 2, No. 6.

Stalling, William. 1997. Data and Computer Communication. New Jersey: Prentice-Hall International, Inc.

Sandige, Ricards., Modern Digital Design. McGraw-Hill Publishing Company.

Stalling, William, 1997, Data and Computer Communication. New Jersey; Prentice-Hall International, Inc.

Stanley, William D., 1994, Operational Amplifier with Linier Integrated Circuit. McGraw-Hill.

Winch, Robert G. 1993, Telecommunication Transmission System. Singapura; McGraw-Hill, Inc.

Black Box Network Services. 2015. HDB3 Encoding http://www.black-box.de/en-de/page/332/hdb3-encoding